|

成功研制以龙芯为内核的税控SOC芯片

概述

税控SoC专用芯片是一款基于GB/T 18240系列标准(参见附录A),集成精简的32位“龙芯1”及外围接口控制模块的专用芯片。

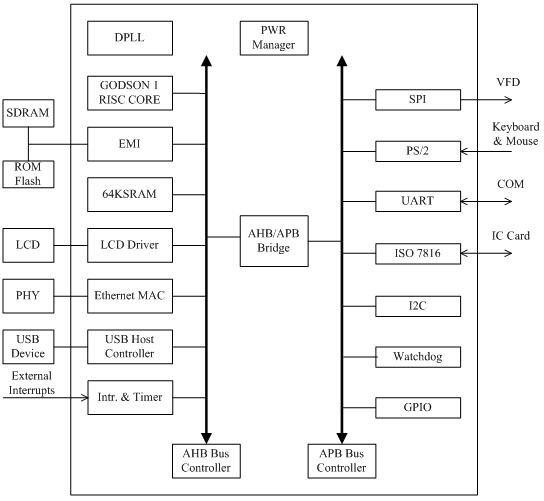

该税控SoC专用芯片以“龙芯1”RISC CPU作为MCU,采用AHB(the Advanced High performance Bus)+APB(the Advanced Peripheral Bus)为片上总线,集成的其余IP模块如表所示。

序号 |

IP名称 |

功能 |

总线接口 |

1 |

SDRAM控制器 |

支持SDRAM作为系统主存 |

AHB |

2 |

ROM/Flash控制器 |

支持Flash作为电子盘 |

3 |

LCD Driver |

驱动营业员的液晶显示屏 |

4 |

10/100Mbps MAC |

支持网络报税 |

5 |

USB 1.1 |

支持USB的电子扫描枪与电子秤(2个端口) |

6 |

SPI |

支持客户VFD屏 |

APB |

7 |

PS/2 |

支持PS/2的键盘与鼠标 |

8 |

UART |

支持串口设备(3个端口),如外接Modem |

9 |

ISO 7816 |

支持税控/用户/税务管理IC卡 |

10 |

I2C |

支持实时时钟RTC |

11 |

Timer |

作为系统资源的定时器 |

12 |

Watchdog |

支持系统死机时自动复位 |

13 |

中断控制器 |

支持外部与内部中断 |

14 |

GPIO |

支持扩展外设 |

税控SoC中集成的IP模块(除MCU外)

技术特征

该芯片的主要技术特征如下:

- 精简的“龙芯1”CPU核

- 32位 RISC CPU

- 五级指令流水

- 8K两路组相联指令Cache与8K两路组相联数据Cache

- EJTAG在线调试

- 片上OHB总线支持:

- 猝发式传输

- 分离事务

- 单拍总线主移交

- 单时钟边沿操作

- 非三态门实现

- 较宽(64/128位)的数据总线配置

- 片上OPB总线支持:

- 不支持猝发式传输

- 一次事务中,地址与控制信号有效

- 在外围总线处于非激活状态时,接口没有功耗

- 通过译码选通来提供计时

- 整个访问中,写数据有效

- 片上64K字节的SRAM

- SDRAM支持:

- 最大支持256MB

- 兼容PC 100/133,工作频率与系统总线的时钟同频

- 可编程的猝发(Burst)长度:1,2,4,8字节与整页

- 支持顺序(Sequential)访问

- 字节使能访问

- 支持SDRAM的模式寄存器配置。

- 方便灵活的访问SDRAM的主接口

- 透明的SDRAM刷新控制

- 透明的SDRAM换行控制

- 在串行方式读写时,连续的块数据访问之间无需额外周期的开销

- SDRAM控制器支持部分字的写原子操作,即读―改―写中间不可打断

- 支持通过本地ROM或Flash引导系统:

- 最大支持64MB

- 数据宽度可以通过配置设为×8或×16

- 支持以块为单位的写、擦除

- 支持读数据和读产品ID

- 低功耗设计考虑,没有命令时,Flash及控制器自动进入待机(Standby)模式

- 支持Deep Power Down模式,使用此模式可以使Flash进一步降低功耗

- LCD 驱动器

- 彩色/单色/灰度LCD面板

- 支持单/双扫描显示

- 片上64K SRAM或系统内存作为显存

- 专用DMA视频数据通道

- 可编程显示屏大小

- 16个灰度等级

- 256彩色

- 10/100Mbps MAC

- 完成IEEE 802.3 MAC层功能

- 32-bit CRC自动生成与校验

- 前置符生成与删除

- 全双工支持

- 10/100 Mbps自适应

- 支持流量控制

- 在半双工时,支持碰撞检测与重发(CSMA/CD)协议

- IEEE 802.3传输介质无关接口(MII)

- 内部RAM 容纳128个 TX/RX缓冲描述符

- 支持中断方式产生事件

- USB 1.1

- 支持低速(1.5Mbps)与全速(12Mbps)两种模式

- 内置DMA通道

- 串行外围接口(SPI)

- 可配置主从模式

- 从模式选择输出

- 模式故障产生错误标志并发出中断请求

- 双缓冲接收器

- 极性和相位可编程的串行时钟

- 可在等待模式下对SPI进行控制

- PS/2接口

- 支持PS/2键盘接口

- 支持PS/2鼠标接口

- UART接口

- 仅工作在FIFO方式

- 在寄存器与功能上兼容NS16550A

- ISO 7816接口

- 半双工操作

- 1个发送缓冲+1个接收缓冲

- 13位波特率选择

- 1/16 bit-time噪声检测

- I2C接口

- 履行双向同步串行协议

- 能够实现多主的操作

- 总线的时钟频率可编程

- 可以产生开始/停止/应答等操作

- 能够对总线的状态进行探测

- 与PHILIPS I2C标准相兼容

- 中断控制器

- 支持软件设置中断

- 支持电平与边沿触发

- 支持中断屏蔽与使能

- GPIO

- GPIO的位数多达48位

- 支持位操作

- 定时器

- 16位计数器及计数器始化寄存器

- 可选择自由计时或倒计时

- 16个可选分频值 ― 20 至 215

- 看门狗

- 16比特计数器及初始化寄存器

- 低功耗模式暂停功能

- 其它

- 片上时钟管理

- 芯片复位配置支持

- 芯片掉电管理

结构框图

SoC的结构框图如图所示。FCR_SOC采用了AHB加APB的两级总线结构,采用完全同步设计,不支持三态总线,采用分开、单向的读写数据总线。AHB总线用来支持高速设备,地址总线宽度为32位,数据总线宽度支持8,16,32位;支持多主从设备。APB用来支持基于寄存器访问的低速设备。地址总线宽度为12位,寻址空间为4K,数据总线宽度为8位;除了总线桥外,其余的IP核均为从设备;只支持单字节访问。AHB与APB两条总线通过总线桥连接在一起,实现两条总线之间的协议转换。

税控SoC体系结构

附录A 税控收款机系列标准

税控收款机系列标准(如下表A.1所示:)发布于2003年6月25日,并于同年10月1日正式实施。

序号 |

名称 |

编号 |

1 |

税控收款机第1部分:机器规范 |

GB 18240.1-2003 |

2 |

税控收款机第2部分:税控IC卡规范 |

GB 18240.2-2003 |

3 |

税控收款机第3部分:税控器规范 |

GB 18240.3-2003 |

4 |

税控收款机第4部分:银行卡受理设备规范 |

GB 18240.4-2003 |

5 |

税控收款机第5部分:税控打印机规范 |

GB 18240.5-2003 |

6 |

税控收款机第6部分:设备编码规范 |

GB 18240.6-2003 |

表A.1:税控收款机系列标准

|